Neil’s breadth of experience enables him to apply formal verification efficiently and thoughtfully within his customers’ design teams. He started his career as a hardware design engineer but later moved to application engineering, supporting FPGA products, before ultimately making the leap to EDA. Neil has deep technical knowledge from working as both a designer and field application engineer. Neil joined the OneSpin team in 2016 and works closely with key customers. Neil Rattray is Senior Field Application Engineer at OneSpin: A Siemens Business and has over 20 years of experience in EDA, supporting both design and verification flows.

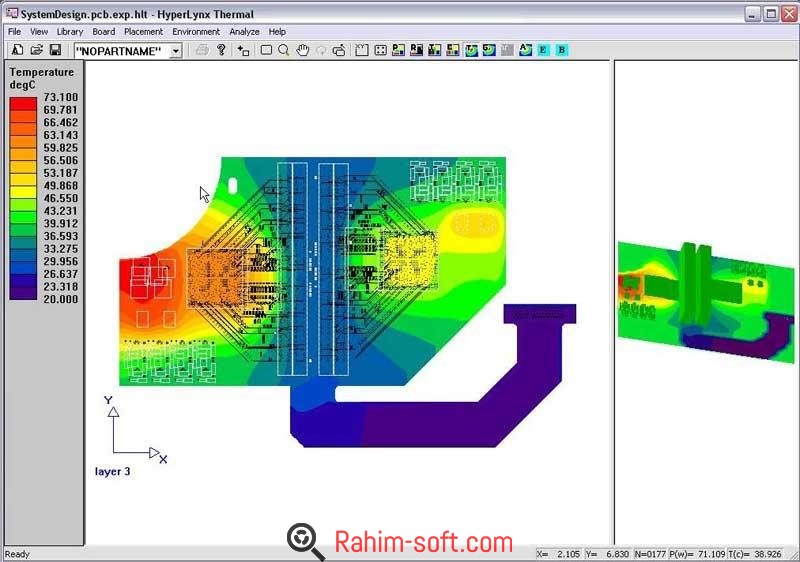

Speaker: Neil Rattray, OneSpin: A Siemens Business As FPGAs become bigger and critical system components, exhaustively verifying the functional equivalence of Register Transfer Level (RTL) code to synthesized netlists and the final placed & routed FPGA designs is mandatory. Formal equivalence checking has been used for ASIC design flows for many years. Systematic design errors, introduced by automated design refinement tools, such as synthesis, can be hard to detect, and damaging if they make it into the final device.

Functional correctness of FPGA synthesis from RTL code to final netlist

0 kommentar(er)

0 kommentar(er)